因為IOT的多項論文提到,IOT的資訊加密的重要性,所以要在電路裡增加加解密,打算要四個加解密方式RSA、AES、DES、3DES,之後擴展為使用PR(Reconfigurable Partitioning)部分可重組技術,可在不斷電情況下將原先的電路進行重新燒錄,並且不引響其他元件的運作,保有硬體原先效能,能夠重複改寫,是個好厲害的技術。傳統嵌入式必須一次性全部掛在電路(之後來做個比較)。

執行環境與配置

測試軟體與建置軟體:Xilinx Vivado2016.4(之後升級為2017) Vivado-SDK

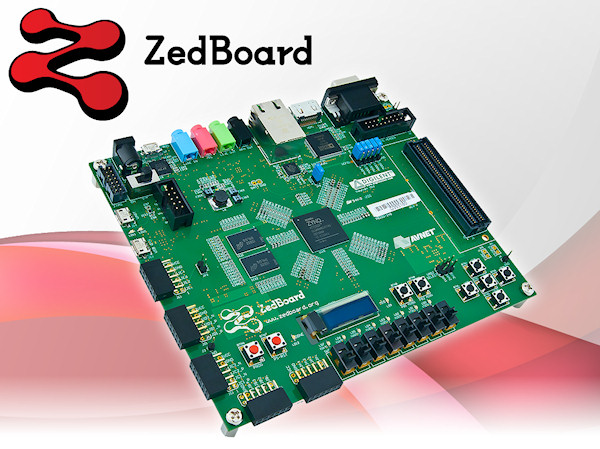

硬體:Xilinx-Zynq 7000 ZedBoard

板子環境(這裡只講到Standalone,要不然還要講到kernel driver。):Xilinx linux3.14(這並不是完整linux環境哦!)

開始製作IP吧!

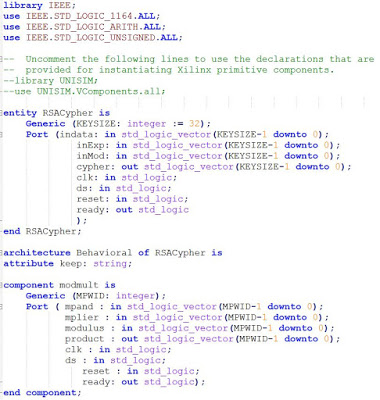

IP為172.168…..(誤!不是這個IP),這裡使用VHDL編寫RSA32的程式碼。

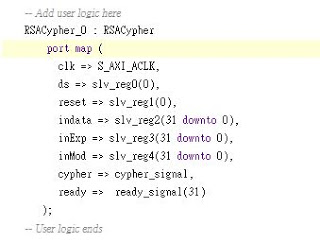

RSA Port部分程式碼檔案:

有了整個的RSA的程式碼,就來把它變成IP吧!

打開vivado 2016併選擇manage ip然後新增IP (檔名我們就取個RSA吧):

建立完成(附註請選擇創造AXI IP 然後透過VHDL我們可以知道需要7個暫存器 clk有系統內建)

接著把RSA的相關程式碼用add source加進去,加進去了就開始撰寫IP得配置和暫存器劃分。

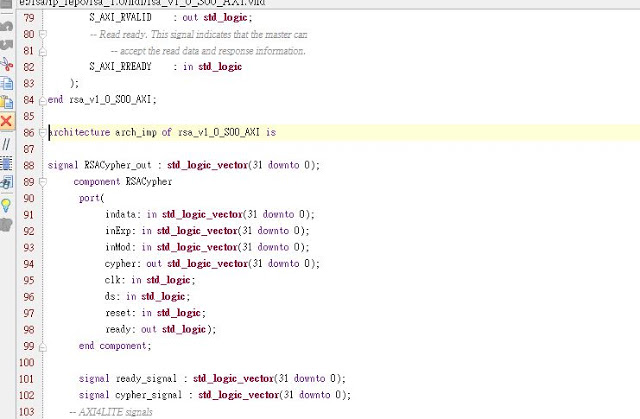

告訴上層的AXI_inst有什麼配置然後所需的位元大小等等……我將2個OUTPUT設2個訊號接點(signal)

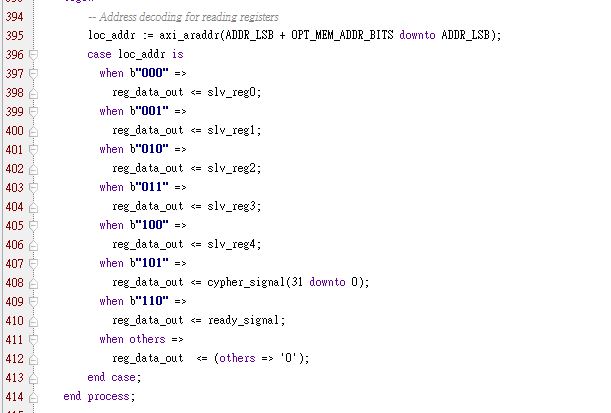

然後來分配暫存器囉,還有加上自己的訊號接點,還有user logic並結合上圖的配置。

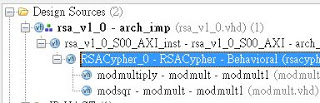

結束存檔會發現一開始匯入的source檔和我們的接線殼合併了(代表吻合囉)!!

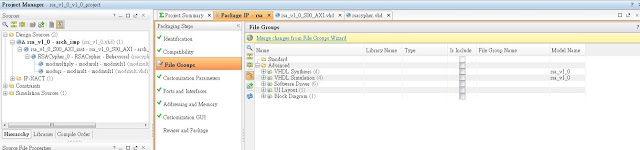

過來就是跑合成run synthesis看看有沒有問題,沒問題之後就能來打包IPpackage ip惹YA(記得merge)

這就完成IP的生成了。

開始匯入IP與設置電路

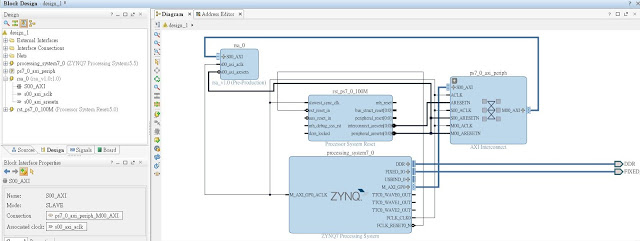

新建一個檔案並選擇我們的Zedboard(xc7z020clg484-1)板子,然後匯入我們的做好的IP,新增一個block design然後把他丟進去加上主控(PS)。

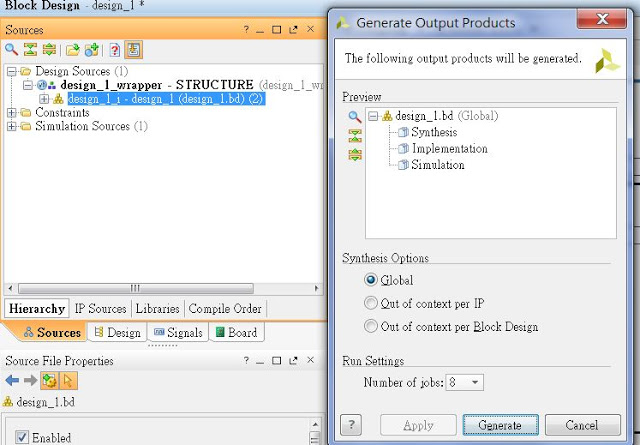

建好之後就來Generate Output Products(生成HDL源文檔和相應端口的約束檔) 和 Create HDL wrapper(生成整個工程的文檔)吧!

開始Run Synthesis -> Run Implemented -> Generate Bitstream -> export Hardware -> launch sdk 轉戰SDK。

SDK做測試

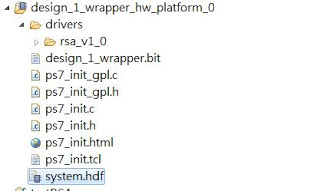

SDK左上角應該就會跑出你剛剛做完的底層(假如沒有在自己匯入檔案吧)

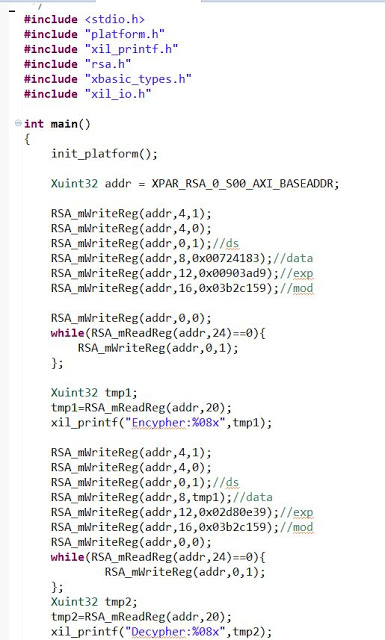

這裡單純只是做Standalone測試ip是否真的能跑起來,所以新增一個hello word project,並改寫裡面的程式碼。

並透過testbench和程式碼判斷哪個暫存器要給什麼值。下面是測資

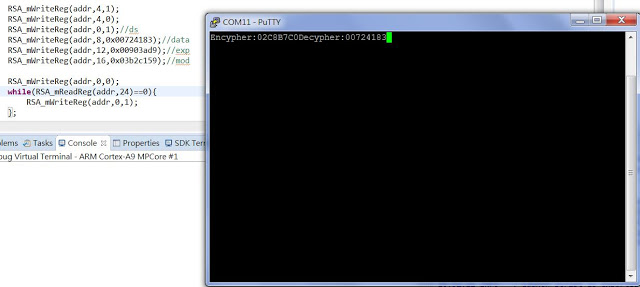

寫完就來測試看看吧!拿出我們貴貴的板子,然後請調板子的jump讓他知道只是下板子不是跑SD卡哦!打開後燒錄我們的底層資訊吧,然後打開putty連進去看狀態並run一下剛剛寫的測試資料。

成功之後就是這樣,很多地方都是提到而已並沒有詳細講下去,有興趣的朋友歡迎討論與指教。