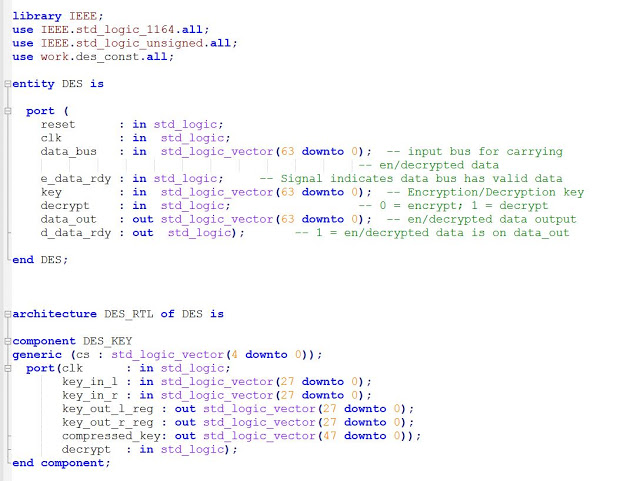

我是利用Xilinx官方提供的xapp270文件來做改寫,原本的文件的DES是利用vhdl的to語法,照之前的AES、RSA的方法很順利成功了,但是在我準備做PR(Reconfigurable Partitioning)發現了一件嚴重的問題!

發生問題!

我們前面的AES RSA皆是用downto的寫法來寫所需的bits數,但是DES是用to的寫法這讓一開始儲存位置不同,所以port無法共用,這在做單一的IP不是問題,也能運作也是正常的作用,但因為我的最後是要用來做PR(Reconfigurable Partitioning),雖然還是有方法能在PR裡面做處理,但是會造成不必要的資源浪費。所以我將DES官方文件的Code改成用downto的方法,

改不難但很麻煩QQ

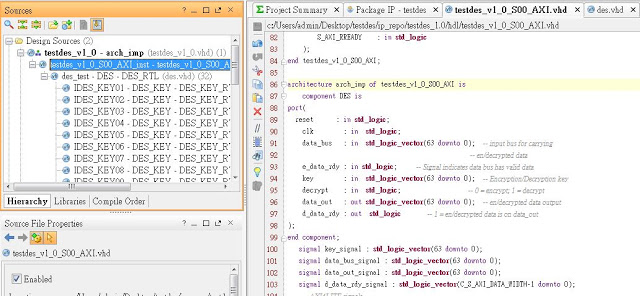

開始製作IP

老樣子創一個新的IP空殼來做IP吧。

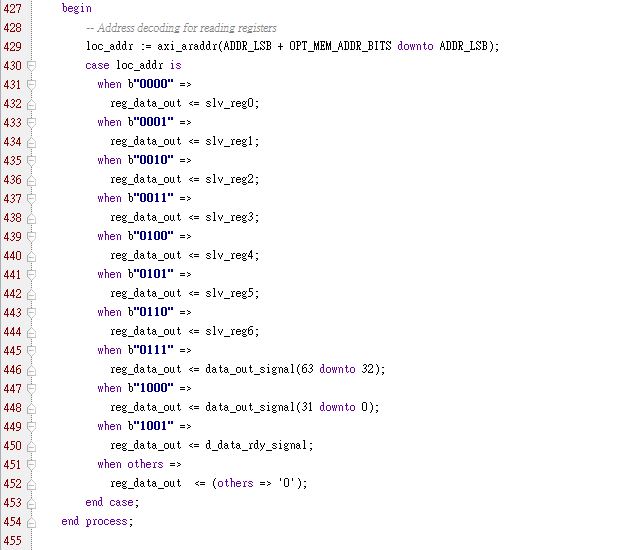

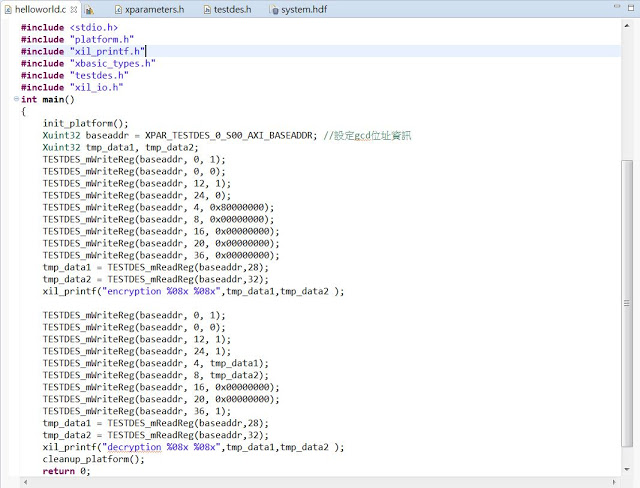

就像之前所說Data Width32 bits,但DES為64所以要拆開來。

這裡不小心粗心,把暫存器7、8寫反了,因為之前to寫法下去改把位置搞反了,所以造成我之後的解密都解失敗。

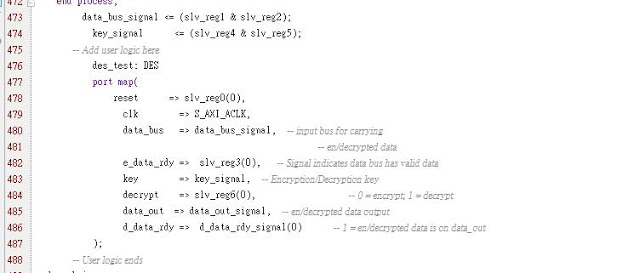

Port map老樣子

開始跑合成,再來就merge和打包成IP,詳情請看前面嚕(偷懶抓到)!

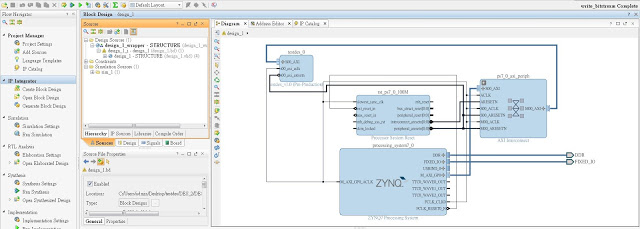

開始匯入IP與設置電路

創建project來把IP放進去。Generate Output Products->Create HDL warpperRun Synthesis -> Run Implemented -> Generate Bitstreamexport Hardware-> launch sdk

請參考前面的做法。

SDK做測試

測試的程式碼。

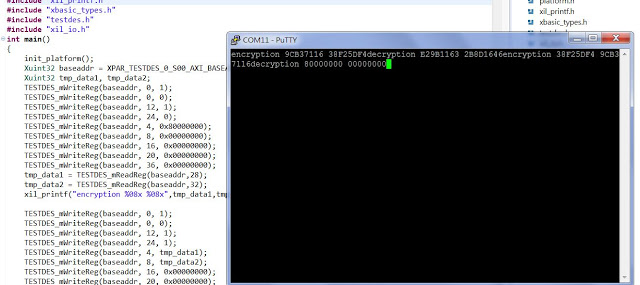

Standalone燒入測試結果。

這讓我知道to downto很容易搞混位置阿!不要造成自己麻煩,還是統一的好。